# **PM7325**

# S/UNI®-ATLAS-3200

# 2488 Mbit/s SATURN® User Network Interface ATM Layer Solution

# **Data Sheet**

Proprietary and Confidential

Preliminary

Issue 4: June 2001

## **Legal Information**

#### Copyright

© 2001 PMC-Sierra, Inc.

The information is proprietary and confidential to PMC-Sierra, Inc., and for its customers' internal use. In any event, you cannot reproduce any part of this document, in any form, without the express written consent of PMC-Sierra, Inc.

PMC-1990553 (P4)

#### **Disclaimer**

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

#### **Trademarks**

S/UNI is a registered trademark of PMC-Sierra, Inc. POS-PHY and SCI-PHY are trademarks of PMC-Sierra, Inc.

#### **Patents**

Relevant patent applications and other patents may also exist.

# **Contacting PMC-Sierra**

PMC-Sierra 8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: (604) 415-6000 Fax: (604) 415-6200

Document Information: document@pmc-sierra.com Corporate Information: info@pmc-sierra.com Technical Support: apps@pmc-sierra.com Web Site: <a href="http://www.pmc-sierra.com">http://www.pmc-sierra.com</a>

# **Public Revision History**

| Issue<br>No. | Issue Date | Details of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Draft 1      | May 1999   | Initial draft.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Draft 2      | June 1999  | Added detailed functional description, register listing, functional timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Draft 3      | Aug 1999   | Aligns with newest 2-chip Embedded-DRAM Solution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Draft 4      | Aug 1999   | Corrected and updated information on UL3 and POS interfaces, per-PHY counting, packet bypass, routing of APS cells. Added Operations Section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Draft 5      | Sep 1999   | TAT and PHYTAT increased to 34 bits. Backwards VCRA and PHYID moved to Linkage Row to help make room. Policing Reserved moved to Row 1 and Parity to Row 0, also to make room. Frame counts added to per-PHY policing. Core Logic Voltage changed to 1.8V. I/O voltage clarified to be 3.3V. Parity added on Address of SRAM as well as data. Pin and block diagrams corrected. PHYID added to Secondary Key. Field B expanded from 11 to 12 bits. Unused bits in Search Table and Linkage Row redistributed to easily accommodate future expansion. Drop_VC does not permit the generation any cells on that connection, whether to OCIF or BCIF. Operation of MCR in GFR policing clarified to explicitly state that MCR operations are performed on frame boundaries only. AUTO_RDI becomes a per-VC bit. DRAM bank number changed to the 2 LSBs of the VCRA rather than the 2 MSBs. Per-PHY counts updated to include counts of EFCI and Timed-Out cells. SRAM, DRAM, per-PHY policing, and PM microprocessor accesses adjusted to access entire records at once, and to have per-field write and Clear-On-Read masks. Basic description of DRAM and SRAM bandwidth allocation added. Gen_halfsecclk bit moved to CP. Slow Background Processing Interrupt added. Capability to switch Input BCIF to Slave mode for use with testers added. Placement of interrupts in Utopia/POS and SDQ blocks changed. Burst length set to a maximum of 256 bytes. Buffer Available thresholds set to a max of 511 bytes. Package changed from 432 TBGA to 576 TBGA to add power/ground balls. Documented separate 1.5V supply for the DRAM. Lower bound of temperature range changed to 0 degrees C. Address map adjusted for easier decode. Added APS cell routing back in. |

| Issue<br>No. | Issue Date | Details of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2            | Feb 2000   | Core logic changed to 1.5V. VC Table parity replaced with CRC-10. "Bwd PM Pending" bit extended for use with Fwd PM Permission cells. VPRMSEL replaced with the more descriptive VP_RM_PTI6. Search key diagrams corrected of typos. Added 1 reserved bit to Source field of Count Rollover FIFO. Fixed TPU_ADDR signal in Figure 6. Fixed PM RAM access ClearOnRd defaults. Removed DMA Request Enable. Moved DMAREQINV to the MCIF. Renamed all references to DMA REQ correctly. Added UPURS_to_OCIF. Added 1 bit to Cell Type field of UPURS and BCIF causation words to add many more cell types. Deleted 1 bit from source ID of the BCIF causation word to make room. Changed all references to AUTOAIS to AUTO_AIS to ensure consistency. Added APStoBCIF and ActDeToBCIF bits. InactivetoUP applies to connections disabled due to CRC errors. Bwd LB cells are not routed to the micro at flow end-points unless the source ID matches the programmed Loopback Location ID, unless the Bwd_LB_to_UP_at_End bit is logic 1. XCLK added to Clock Activity monitor. Device now powers-up in reset, must be held there to allow the DRAM to settle for 200 us. Per-PHY counting bit descriptions of Cnt_Inv_OAM and Cnt_Rsvd_VCI_PTI corrected. Added VPC Counting. Added Policing Rollover FIFO Enable bits. Added FREE[7:0]. Added LBtoOCIF. Added RxPHYTxPHY internal test bit. Made Maximum Frame Length test disabled if MFL = all ones, to match ATLAS. Added feature for allowing CC alarms to not generate COS entries, via the OAM Config status bit. Added a globally enabled feature that permits Bwd PM cells to carry the Fwd PM Cell's time stamp, if the Bwd PM cell is able to be generated immediately. Added Don't-Touch designation for OC-48C cascading. SDQ register map substantially reorganized. Meanings of Buffer Available and Data Available thresholds changed slightly. SDQ per-PHY counts reduced to 4 bits; aggregate cell count increased to 32 bits. Added generic names for UL3/PL3 pins for easier reference. INBANDADDR function added to PL3 blocks to accommodate single-PHY opera |

| Issue<br>No. | Issue Date | Details of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3            | Oct 2000   | Clarified that UPURS_to_OCIF overrides XPREPO, and that PROC_CELL or PROCESS_PHY overrides XPREPO. Absolute Maximum ratings updated (SRAM interface specced relative to VDD25; absolute min voltage changed to —0.3, absolute max to VDDX+0.3, Max current on pins reduced to 10mA). Clarified translation options to BCIF. Added Mkt_NUM register in ID register. Added dropped-cells counter on MCIF. Added note that reserved fields in the Search and Linkage tables must be programmed to logic 0 for proper operation. Adjusted format of Count Rollover FIFO. Added extra notes about the restriction on the 2 LSBs of the VPC Pointer. Changed Inact_on_Par_Err to Inact_on_DRAM_Err. Corrected RxL, TxL Indirect Address register. Increased min prop delay on UL3/PL3 to 1.5 ns. Changed package from 576 to 768 TBGA. Split SCLK_O into SYSCLK_O and SRAMCLK_O. Added Timeout_To_UP bit to Register 0x100. Renamed AIS_VPC to Sending_AIS. Changed COS fifo description to show all bits. Renamed a few of the CP interrupts to have more expressive names. Clarified that Returned LB cells are translated like other generated cells (RDI and Bwd PM). Renamed F4toF5AIS to F4toF5OAM to reflect the fact it controls both AIS and RDI. Clarified the difference between Block_Ptr and FIFO_Number in the SDQ Configuration description. Clarified that Ete Loopback cells are looped back at end-to-end points if their LLID = all 1, or if it matches the LLID of the end point. Modified Sat_PM_BIP16 to Sat_Fast_PM_Counts and made it affect the Lost PM Cell Counts as well. Changed drop_vc to have no effect on the generation of OAM cells to the BCIF. F5 AIS cells due to F4 AIS carry the F4 AIS defect location/type. When F4-to-F5, per-PHY or CC AIS is generated, then if ATLAS is within a segment for that VC, both Segment and ETE AIS are generated. Changed "SCSB" to "SCEB" for consistency. Fixed an inconsistency in fm_interrupt_enable naming. Corrected description of EFCI count. Updated PM documentation to better reflect behavior with SECBs. Added documentation that Count Roll |

| Issue<br>No. | Issue Date | Details of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4            |            | Revealed COS_CC_DIS bit. Changed ATM_FIELD default to 0x00. Documented the fact that micro accesses can take as long as 40 cycles (for a read) or 90 cycles (for a write) in certain unusual cases. IBCIF and OBCIF default to odd parity, not even parity. PHY and Link blocks should be left in their default state when not being used. Typo to INSRST corrected. Direction of OBCIF, IBCIF clocks in figures 5,6,7,8 corrected. INSRDY documentation corrected to say that INSRDY stays high until a full cell has been written in. Halfsecclk input pin description altered to point correctly to the gen_halfsecclk bit. Documented the proper default state for the one-second CC, AIS, and Failure counts. Updated Boundary Scan description to match BSDL notation. Clarified that SDQ, PHY, and LINK interrupts are only asserted for interrupts that are enabled at the TSB level. Clarified that min freq for icif_clk and ocif_clk is 75 MHz, but that full bandwidth is only guaranteed at 104 MHz. Block size of 1 in Bypass SDQ explicitly not supported. OBCIF dropped-cells counter exposed, with a comment about the total BCIF capacity. VC_to_BCIF documented with the overflow mechanism. RxPhy calendar now states that it should be set to at least 64 entries, and preferably as close to 128 entries as possible, for maximum efficiency. Clarified that LBtoOCIF also overrides discarding due to LB_Route functionality. Clarified DLLRUN Bit functionality. Deleted XferErrToUP function; parity errors and rlp_err/tpp_err indications have no effect on ATM cells (beyond the assertion of an interrupt for a parity error). Recommended that the FLUSH bit be set for all disabled FIFOs, to eliminate spurious interrupts. Clarified that CntUndefOAM has no effect on OAMERRI. Increased maximum secondary search depth to 18. Changed PL3 loading to 30 pf to match the PL3 standard. Changed voltage rail spec. to +/-5%. Clarified that FM_to_UP does not control loopback cells, since LB_ROUTE does this. Added TM0 Details. Added thermal information. Specified max power at 3.0 W. I |

# **Table of Contents**

| Pul  | olic Re | vision F   | listory                                     | 4  |

|------|---------|------------|---------------------------------------------|----|

| Tab  | le of C | Contents   | 3                                           | 8  |

| List | of Re   | gisters.   |                                             | 12 |

| List | of Fig  | gures      |                                             | 18 |

| List | of Tal  | bles       |                                             | 20 |

| 1    | Defin   | itions     |                                             | 22 |

| 2    | Featu   | ıres       |                                             | 25 |

|      | 2.1     | Policing   | g                                           | 27 |

|      | 2.2     | Perforn    | nance Management                            | 28 |

|      | 2.3     | Cell Co    | punting                                     | 29 |

| 3    | Appli   | cations.   |                                             | 30 |

| 4    | Refer   | ences      |                                             | 31 |

| 5    | Appli   | cation E   | xamples                                     | 32 |

|      | 5.1     | Cascad     | ding                                        | 32 |

|      | 5.2     | RAM C      | Configurations                              | 33 |

| 6    | Block   | Diagra     | m                                           | 34 |

| 7    | Desc    | ription    |                                             | 35 |

| 8    | Pin D   | iagram     |                                             | 38 |

| 9    | Pin D   | escription | on                                          | 45 |

| 10   | Func    | tional De  | escription                                  | 63 |

|      | 10.1    | Input a    | nd Output Interfaces                        | 63 |

|      |         | 10.1.1     | Ingress Mode with UTOPIA Level 3 Signaling  | 63 |

|      |         | 10.1.2     | Egress Mode with UTOPIA Level 3 Signaling   | 65 |

|      |         | 10.1.3     | Ingress Mode with POS-PHY Level 3 Signaling | 66 |

|      |         | 10.1.4     | Egress Mode with POS_PHY Level 3 Signaling  | 68 |

|      |         | 10.1.5     | Polling and Servicing Calendar              | 69 |

|      |         | 10.1.6     | PHY Mapping                                 | 71 |

|      |         | 10.1.7     | Scalable Data Queue                         | 71 |

|      |         | 10.1.8     | Packet-Bypass Mode                          | 72 |

|      |         | 10.1.9     | ATM Cell Format                             | 72 |

|      | 10.2    | Conne      | ction Identification                        | 73 |

|      |         | 10.2.1     | Search Table Data Structure                 | 77 |

|      | 10.3    | VC Lin     | kage Table                                  | 79 |

11

| 10.4  | VC Re     | cord Table                                                | 80  |

|-------|-----------|-----------------------------------------------------------|-----|

| 10.5  | Cell Pr   | ocessing                                                  | 80  |

| 10.6  | Heade     | Translation                                               | 90  |

| 10.7  | Cell Ra   | te Policing                                               | 91  |

|       | 10.7.1    | Per-VC Policing                                           | 91  |

|       | 10.7.2    | Per-PHY Policing                                          | 98  |

|       | 10.7.3    | Guaranteed Frame Rate Policing                            | 101 |

| 10.8  | Cell Co   | punting                                                   | 103 |

| 10.9  | Operat    | ions, Administration and Maintenance (OAM) Cell Servicing | 104 |

|       | 10.9.1    | Fault Management Cells                                    | 105 |

|       | 10.9.2    | Loopback Cells                                            | 107 |

|       | 10.9.3    | Activation/Deactivation Cells                             | 107 |

|       | 10.9.4    | System Management Cells                                   | 107 |

|       | 10.9.5    | Automated Protection Switching Cells                      | 108 |

|       | 10.9.6    | Resource Management Cells                                 | 108 |

| 10.10 | F4 to F   | 5 OAM Processing                                          | 108 |

| 10.11 | F5 to F   | 4 OAM Processing                                          | 116 |

| 10.12 | 2 Constra | aints on F5 and F4 VC Table Record Addresses              | 116 |

| 10.13 | Backgr    | ound Processes                                            | 117 |

| 10.14 | Perforn   | nance Management                                          | 118 |

|       | 10.14.1   | Performance Management Flows                              | 118 |

|       |           | Performance Management Record Table                       |     |

| 10.15 | Change    | e of Connection State FIFO                                | 129 |

| 10.16 | Count I   | Rollover FIFO                                             | 130 |

| 10.17 | Cell Ro   | outing                                                    | 133 |

|       | 10.17.1   | Output Backward OAM Cell Interface                        | 134 |

|       | 10.17.2   | Input Backward OAM Cell Interface                         | 138 |

|       | 10.17.3   | Internal DRAM Access                                      | 139 |

|       | 10.17.4   | Writing Cells                                             | 140 |

|       | 10.17.5   | Reading Cells                                             | 141 |

| 10.18 | JTAG 1    | Test Access Port                                          | 143 |

| Norm  | al Mode   | Register Description                                      | 144 |

| 11.1  | List of I | Registers                                                 | 144 |

| 11.2  | Core R    | egisters                                                  | 151 |

| 11.3  | Microp    | rocessor Cell Interface                                   | 169 |

|    | 11.4   | Backwa    | ard Cell Interface               | 176 |

|----|--------|-----------|----------------------------------|-----|

|    | 11.5   | Cell Pr   | ocessor                          | 190 |

|    |        | 11.5.1    | General Configuration and Status | 190 |

|    |        | 11.5.2    | Search                           | 219 |

|    |        | 11.5.3    | VC Table                         | 225 |

|    |        | 11.5.4    | Policing                         | 242 |

|    |        | 11.5.5    | OAM Fault Management             | 259 |

|    |        | 11.5.6    | OAM Loopback                     | 270 |

|    |        | 11.5.7    | OAM Performance Management       | 272 |

|    |        | 11.5.8    | Change of Connection State FIFO  | 286 |

|    |        | 11.5.9    | Count Rollover FIFO              | 288 |

|    |        | 11.5.10   | Per PHY Statistics               | 291 |

|    | 11.6   | Rx Link   | < Interface                      | 308 |

|    | 11.7   | Tx PH     | Y Interface                      | 318 |

|    | 11.8   | Input S   | calable Data Queue               | 323 |

|    | 11.9   | Rx PH     | Y Interface                      | 334 |

|    | 11.10  | Tx Link   | Interface                        | 344 |

|    | 11.11  | Output    | Scalable Data Queue              | 354 |

|    | 11.12  | Packet    | Bypass Scalable Data Queue       | 365 |

| 12 | Test I | eatures   | s Description                    | 376 |

|    | 12.1   | Test Mo   | ode 0 Details                    | 378 |

|    | 12.2   | JTAG 1    | Fest Port                        | 379 |

| 13 | Opera  | ations    |                                  | 390 |

|    | 13.1   | Configu   | uring the Scalable Data Queue    | 390 |

|    | 13.2   | JTAG S    | Support                          | 392 |

|    |        | 13.2.1    | TAP Controller                   | 394 |

|    | 13.3   | Board I   | Design Recommendations           | 396 |

| 4  | Func   | tional Ti | ming                             | 397 |

|    | 14.1   | POS-P     | HY Level 3                       | 397 |

|    |        | 14.1.1    | Ingress Packet Interface         | 397 |

|    |        | 14.1.2    | Egress Packet Interface          | 403 |

|    | 14.2   | UTOPI     | A Level 3                        | 408 |

|    |        | 14.2.1    | Ingress UL3 Interface            | 409 |

|    |        | 14.2.2    | Egress UL3 Interface             | 412 |

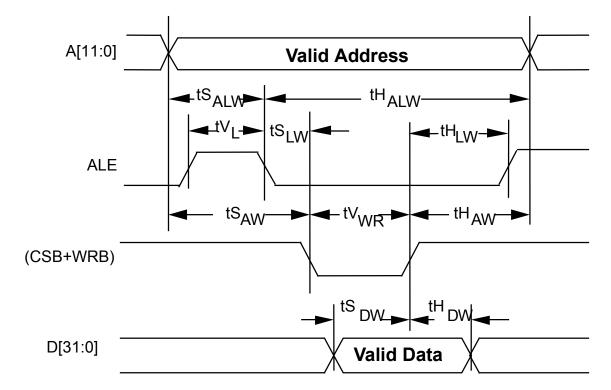

|    | 14.3   | SRAM      | Interface                        | 415 |

|     | 14.4  | Backwards Cell Interface              | 417 |

|-----|-------|---------------------------------------|-----|

| 15  | Abso  | lute Maximum Ratings                  | 418 |

| 16  | D.C.  | Characteristics                       | 419 |

| 17  | A.C.  | Timing Characteristics                | 421 |

|     | 17.1  | Conditions                            | 421 |

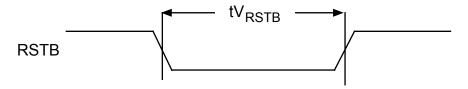

|     | 17.2  | Reset Timing                          | 421 |

|     | 17.3  | Half-Second Clock Timing              | 421 |

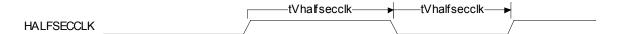

|     | 17.4  | Microprocessor Interface Read Timing  | 421 |

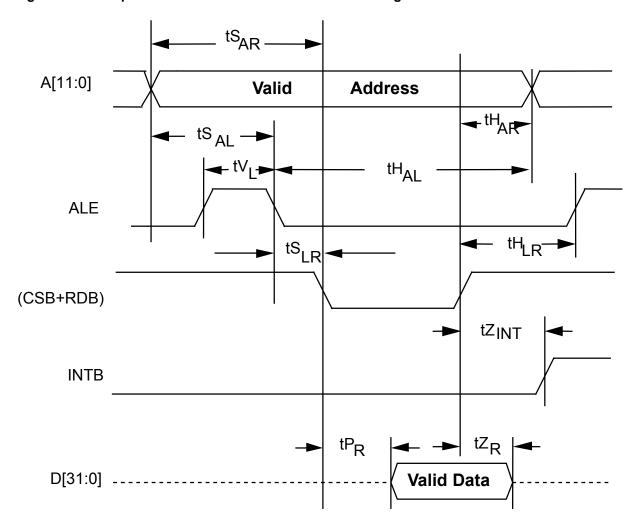

|     | 17.5  | Microprocessor Interface Write Timing | 423 |

|     | 17.6  | UL3/PL3 Interface Timing              | 424 |

|     | 17.7  | BCIF Interface Timing                 | 425 |

|     | 17.8  | SRAM Interface Timing                 | 426 |

|     | 17.9  | JTAG Interface Timing                 | 426 |

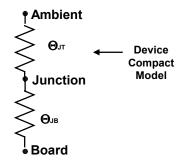

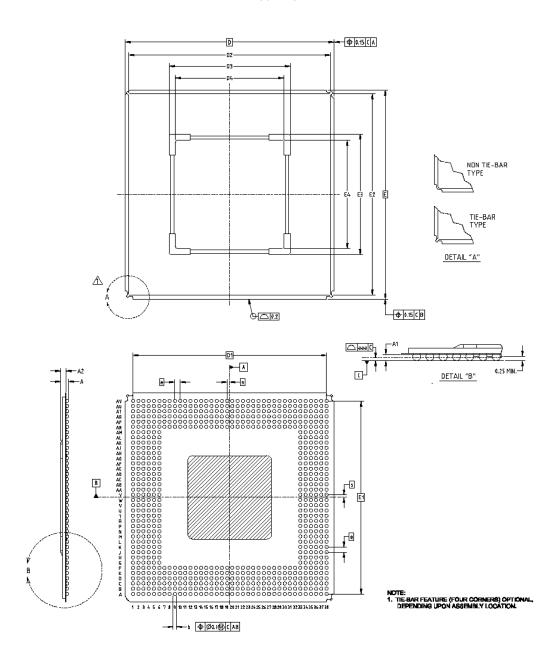

| 18  | Orde  | ring and Thermal Information          | 429 |

|     | 18.1  | Ordering Information                  | 429 |

|     | 18.2  | Thermal Information                   | 429 |

| 19  | Mech  | nanical Information                   | 429 |

| Not | es 43 | 2                                     |     |

# **List of Registers**

| Register 0x000: | S/UNI-ATLAS-3200 Master Configuration And Reset          | 151 |

|-----------------|----------------------------------------------------------|-----|

| Register 0x001: | S/UNI-ATLAS-3200 Identity / Load Counts                  | 154 |

| Register 0x002: | Master Interrupt Status #1                               | 156 |

| Register 0x003: | Master Interrupt Status #2                               | 162 |

| Register 0x004: | Master Interrupt Enable #1                               | 164 |

| Register 0x005: | Master Interrupt Enable #2                               | 166 |

| Register 0x006: | Master Clock Monitor                                     | 167 |

| Register 0x020: | Microprocessor Cell Interface Control and Status         | 169 |

| Register 0x021: | Microprocessor Cell Data                                 | 173 |

| Register 0x022: | MCIF Dropped Cells Counter                               | 175 |

| Register 0x030: | Input Backwards Cell Interface Configuration             | 176 |

| Register 0x031: | IBCIF Dropped Cells Counter                              | 178 |

| Register 0x032: | IBCIF Read Cells Counter                                 | 179 |

| Register 0x038: | Output Backwards Cell Interface Configuration            | 180 |

| Register 0x039: | OBCIF Dropped Cells Counter                              | 181 |

| Register 0x03A: | OBCIF Read Cells Counter                                 | 182 |

| Register 0x040: | SYSCLK Delay Locked Loop Register 1                      | 183 |

| Register 0x041: | SYSCLK DLL Register 2                                    | 185 |

| Register 0x042: | SYSCLK DLL Register 3                                    | 186 |

| Register 0x043: | SYSCLK DLL Register 4                                    | 187 |

| Register 0x100: | Cell Processor Configuration                             | 190 |

| Register 0x101: | Cell Processor Routing Configuration                     | 197 |

| Register 0x102: | Cell Counting Configuration                              | 203 |

| Register 0x104: | Backward Cell Interface Pacing and Head of Line Blocking | 205 |

| Register 0x105: | Per-PHY Processing Enable 1                              | 207 |

| Register 0x106: | Per-PHY Processing Enable 2                              | 209 |

| Register 0x107: | AIS/CC Pacing and Head of Line Blocking                  | 211 |

| Register 0x108: | Fwd PM Pacing and Head of Line Blocking                  | 213 |

| Register 0x109: | Inoperative PHY Declaration Period and Indications       | 215 |

| Register 0x10A: | Inoperative PHY Indications                              | 217 |

| Register 0x10B: | Search Engine Configuration                              | 219 |

| Register 0x10C: | SRAM Access Control                                      | 221 |

| Register 0x10D: | SRAM Data LSW (SRAM Data[31:0])                          | 223 |

| Register 0x10E: | SRAM Data MSW (SRAM Data [63:32])                     | 224 |

|-----------------|-------------------------------------------------------|-----|

| Register 0x110: | VC Table Maximum Index                                | 225 |

| Register 0x111: | VC Table Access Control                               | 226 |

| Register 0x112: | VC Table Write Enable 1                               | 229 |

| Register 0x113: | VC Table Write Enable 2                               | 231 |

| Register 0x114: | VC Table Data Row 0, Word 0 (LSW) (RAM Data [31:0])   | 232 |

| Register 0x115: | VC Table Data Row 0, Word 1 (RAM Data [63:32])        | 233 |

| Register 0x116: | VC Table Data Row 0, Word 2 (RAM Data [95:64])        | 234 |

| Register 0x117: | VC Table Data Row 0, Word 3 (MSW) (RAM Data [127:96]) | 235 |

| Register 0x118: | VC Table Data Row 1, Word 0 (LSW) (RAM Data [31:0])   | 236 |

| Register 0x119: | VC Table Data Row 1, Word 1 (RAM Data [63:32])        | 236 |

| Register 0x11A: | VC Table Data Row 1, Word 2 (RAM Data [95:64])        | 236 |

| Register 0x11B: | VC Table Data Row 1, Word 3 (MSW) (RAM Data [127:96]) | 236 |

| Register 0x11C: | VC Table Data Row 2, Word 0 (LSW) (RAM Data [31:0])   | 237 |

| Register 0x11D: | VC Table Data Row 2, Word 1 (RAM Data [63:32])        | 237 |

| Register 0x11E: | VC Table Data Row 2, Word 2 (RAM Data [95:64])        | 237 |

| Register 0x11F: | VC Table Data Row 2, Word 3 (MSW) (RAM Data [127:96]) | 237 |

| Register 0x120: | VC Table Data Row 3, Word 0 (LSW) (RAM Data [31:0])   | 238 |

| Register 0x121: | VC Table Data Row 3, Word 1 (RAM Data [63:32])        | 238 |

| Register 0x122: | VC Table Data Row 3, Word 2 (RAM Data [95:64])        | 238 |

| Register 0x123: | VC Table Data Row 3, Word 3 (MSW) (RAM Data [127:96]) | 238 |

| Register 0x124: | VC Table Data Row 4 Word 0 (LSW) (RAM Data [31:0])    | 239 |

| Register 0x125: | VC Table Data Row 4, Word 1 (RAM Data [63:32])        | 239 |

| Register 0x126: | VC Table Data Row 4, Word 2 (RAM Data [95:64])        | 239 |

| Register 0x127: | VC Table Data Row 4, Word 3 (MSW) (RAM Data [127:96]) | 239 |

| Register 0x128: | VC Table Data Row 5 Word 0 (LSW) (RAM Data [31:0])    | 240 |

| Register 0x129: | VC Table Data Row 5, Word 1 (RAM Data [63:32])        | 240 |

| Register 0x12A: | VC Table Data Row 5, Word 2 (RAM Data [95:64])        | 240 |

| Register 0x12B: | VC Table Data Row 5, Word 3 (MSW) (RAM Data [127:96]) | 240 |

| Register 0x12C: | VC Table Data Row 6 Word 0 (LSW) (RAM Data [31:0])    | 241 |

| Register 0x12D: | VC Table Data Row 6, Word 1 (RAM Data [63:32])        | 241 |

| Register 0x12E: | VC Table Data Row 6, Word 2 (RAM Data [95:64])        | 241 |

| Register 0x12F: | VC Table Data Row 6, Word 3 (MSW) (RAM Data [127:96]) | 241 |

| Register 0x130: | Per-VC Non-Compliant Cell Counting Configuration      | 242 |

| Register 0x131: | Connection Policing Configuration 1 & 2               | 244 |

| Register 0x132: | Connection Policing Configuration 3 & 4                               | 245 |

|-----------------|-----------------------------------------------------------------------|-----|

| Register 0x133: | Connection Policing Configuration 5 & 6                               | 245 |

| Register 0x134: | Connection Policing Configuration 7 & 8                               | 245 |

| Register 0x140: | PHY Policing Enable 1                                                 | 246 |

| Register 0x141: | PHY Policing Enable 2                                                 | 248 |

| Register 0x142: | PHY Policing Configuration                                            | 249 |

| Register 0x143: | Per-PHY Non-Compliant Cell Counting Configuration                     | 251 |

| Register 0x144: | PHY Policing RAM Address and Access Control                           | 252 |

| Register 0x145: | PHY Policing RAM Data Row 0                                           | 255 |

| Register 0x146: | PHY Policing RAM Data Row 1                                           | 256 |

| Register 0x147: | PHY Policing RAM Data Row 2                                           | 257 |

| Register 0x148: | PHY Policing RAM Data Row 3                                           | 258 |

| Register 0x151: | OAM Defect Location Octets 3 to 0                                     | 259 |

| Register 0x152: | Defect Location Octets 7 to 4                                         | 260 |

| Register 0x153: | Defect Location Octets 11 to 8                                        | 260 |

| Register 0x154: | Defect Location Octets 15 to 12                                       | 260 |

| Register 0x155: | Per-PHY AIS Cell Generation Control 1                                 | 261 |

| Register 0x156: | Per-PHY AIS Cell Generation Control 2                                 | 263 |

| Register 0x157: | Per-PHY RDI Cell Generation Control 1                                 | 264 |

| Register 0x158: | Per-PHY RDI Cell Generation Control 2                                 | 266 |

| Register 0x159: | Per-PHY APS Indication 1                                              | 267 |

| Register 0x15A: | Per-PHY APS Indication 2                                              | 269 |

| Register 0x160: | OAM Loopback Location ID Octets 3 to 0                                | 270 |

| Register 0x161: | Loopback Location ID Octets 7 to 4                                    | 271 |

| Register 0x162: | Loopback Location ID Octets 11 to 8                                   | 271 |

| Register 0x163: | Loopback Location ID Octets 15 to 12                                  | 271 |

|                 | Performance Management RAM Record Address, Word Select Access Control | 272 |

| Register 0x171: | Performance Management RAM Row 0 Word 0 (LSW)                         | 274 |

| Register 0x172: | Performance Management RAM Row 0 Word 1                               | 275 |

| Register 0x173: | Performance Management RAM Row 0 Word 2 (MSW)                         | 276 |

| Register 0x174: | Performance Management RAM Row 1 Word 0 (LSW)                         | 277 |

| Register 0x175: | Performance Management RAM Row 1 Word 1                               | 277 |

| Register 0x176: | Performance Management RAM Row 1 Word 2 (MSW)                         | 277 |

| Register 0x177: | Performance Management RAM Row 2 Word 0 (LSW)                         | 278 |

| Register 0x178: | Performance Management RAM Row 2 Word 1                  | 278 |

|-----------------|----------------------------------------------------------|-----|

| Register 0x179: | Performance Management RAM Row 2 Word 2 (MSW)            | 278 |

| Register 0x17A: | Performance Management RAM Row 3 Word 0 (LSW)            | 279 |

| Register 0x17B: | Performance Management RAM Row 3 Word 1                  | 279 |

| Register 0x17C: | Performance Management RAM Row 3 Word 2 (MSW)            | 279 |

| Register 0x17D: | Performance Management RAM Row 4 Word 0 (LSW)            | 280 |

| Register 0x17E: | Performance Management RAM Row 4 Word 1                  | 280 |

| Register 0x17F: | Performance Management RAM Row 4 Word 2 (MSW)            | 280 |

| Register 0x180: | Performance Management RAM Row 5 Word 0 (LSW)            | 281 |

| Register 0x181: | Performance Management RAM Row 5 Word 1                  | 281 |

| Register 0x182: | Performance Management RAM Row 5 Word 2 (MSW)            | 281 |

| Register 0x183: | Performance Management RAM Row 6 Word 0 (LSW)            | 282 |

| Register 0x184: | Performance Management RAM Row 6 Word 1                  | 282 |

| Register 0x185: | Performance Management RAM Row 6 Word 2 (MSW)            | 282 |

| Register 0x186: | Performance Management RAM Row 7 Word 0 (LSW)            | 283 |

| Register 0x187: | Performance Management RAM Row 7 Word 1                  | 283 |

| Register 0x188: | Performance Management RAM Row 7 Word 2 (MSW)            | 283 |

| Register 0x189: | Performance Management Threshold A                       | 284 |

| Register 0x18A: | Performance Management Threshold B                       | 285 |

| Register 0x18B: | Performance Management Threshold C                       | 285 |

| Register 0x18C: | Performance Management Threshold D                       | 285 |

| Register 0x190: | VC Table Change of Connection State FIFO Status          | 286 |

| Register 0x191: | VC Table Change of Connection State FIFO Data            | 287 |

| Register 0x198: | Count Rollover FIFO Status                               | 288 |

| Register 0x199: | Count Rollover FIFO Data                                 | 289 |

| Register 0x1A0: | Per-PHY Counter Configuration                            | 291 |

| Register 0x1A1: | Per-PHY Counter Control                                  | 293 |

| Register 0x1A8: | Per-PHY CLP0 Cell Count Holding Register                 | 296 |

| Register 0x1A9: | Per PHY CLP1 Cell Count Holding Register                 | 298 |

| Register 0x1AA: | Per PHY Valid RM Cell Counts Holding Register            | 299 |

| Register 0x1AB: | Per PHY Valid OAM Cell Counts Holding Register           | 300 |

| Register 0x1AC: | Per PHY Errored OAM/RM Cell Counts Holding Register      | 301 |

| Register 0x1AD: | Per PHY Invalid VPI/VCI/PTI Cell Counts Holding Register | 302 |

| Register 0x1AE: | Per-PHY EFCI/Non-Zero GFC Cell Count Holding Register    | 303 |

| Register 0x1AF: | Per-PHY Timed-Out Cell Count Holding Register            | 304 |

| Register 0x1B0: | Per PHY Last Unknown VPI & VCI Holding Register | .305 |

|-----------------|-------------------------------------------------|------|

| Register 0x1C0: | Reserved                                        | .307 |

| Register 0x200: | RxL Configuration                               | .308 |

| Register 0x201: | RxL Interrupt Enable                            | .310 |

| Register 0x202: | RxL Interrupt                                   | .311 |

| Register 0x208: | RxL PHY Indirect Address                        | .312 |

| Register 0x209: | RxL PHY Indirect Data                           | .313 |

| Register 0x20A: | RxL Calendar Length                             | .314 |

| Register 0x20B: | RxL Calendar Indirect Address and Data          | .315 |

| Register 0x20C: | RxL Data Type Field                             | .317 |

| Register 0x220: | TxP Configuration                               | .318 |

| Register 0x221: | TxP Interrupt                                   | .320 |

| Register 0x222: | TxP Interrupt Enable                            | .321 |

| Register 0x223: | TxP Data Type Field                             | .322 |

| Register 0x240: | Input SDQ Control                               | .323 |

| Register 0x241: | Input SDQ Interrupts                            | .324 |

| Register 0x242: | Input SDQ Interrupt ID                          | .326 |

| Register 0x244: | Input SDQ Indirect Address                      | .327 |

| Register 0x245: | Input SDQ Indirect Configuration                | .329 |

| Register 0x246: | Input SDQ Cells and Packets Count               | .331 |

| Register 0x247: | Input SDQ Cells Accepted Aggregate Count        | .332 |

| Register 0x248: | Input SDQ Cells Dropped Aggregate Count         | .333 |

| Register 0x260: | RxP Configuration                               | .334 |

| Register 0x261: | RxP Interrupt                                   | .336 |

| Register 0x262: | RxP Interrupt Enable                            | .337 |

| Register 0x263: | RxP PHY Indirect Address and Data               | .338 |

| Register 0x264: | RxP Calendar Length                             | .340 |

| Register 0x265: | RxP Calendar Indirect Address and Data          | .341 |

| Register 0x266: | RxP Data Type Field                             | .343 |

| Register 0x280: | TxL Configuration                               | .344 |

| Register 0x281: | TxL Interrupt Enable                            | .346 |

| Register 0x282: | TxL Interrupt                                   | .347 |

| Register 0x286: | TxL Data Type Field                             | .348 |

| Register 0x288: | TxL PHY Indirect Address                        | .349 |

| Register 0x289: | TxL PHY Indirect Data                           | .350 |

| Register 0x28A: | TxL Calendar Length                       | 351 |

|-----------------|-------------------------------------------|-----|

| Register 0x28B: | TxL Calendar Indirect Address and Data    | 352 |

| Register 0x2A0: | Output SDQ Control                        | 354 |

| Register 0x2A1: | Output SDQ Interrupts                     | 355 |

| Register 0x2A2: | Output SDQ Interrupt ID                   | 357 |

| Register 0x2A4: | Output SDQ Indirect Address               | 358 |

| Register 0x2A5: | Output SDQ Indirect Configuration         | 360 |

| Register 0x2A6: | Output SDQ Cells and Packets Count        | 362 |

| Register 0x2A7: | Output SDQ Cells Accepted Aggregate Count | 363 |

| Register 0x2A8: | Output SDQ Cells Dropped Aggregate Count  | 364 |

| Register 0x2C0: | Bypass SDQ Control                        | 365 |

| Register 0x2C1: | Bypass SDQ Interrupts                     | 366 |

| Register 0x2C2: | Bypass SDQ Interrupt ID                   | 368 |

| Register 0x2C4: | Bypass SDQ Indirect Address               | 369 |

| Register 0x2C5: | Bypass SDQ Indirect Configuration         | 371 |

| Register 0x2C6: | Bypass SDQ Cells and Packets Count        | 373 |

| Register 0x2C7: | Bypass SDQ Cells Accepted Aggregate Count | 374 |

| Register 0x2C8: | Bypass SDQ Cells Dropped Aggregate Count  | 375 |

| Register 0x800: | Master Test                               | 377 |

# **List of Figures**

| Figure 1  | S/UNI-ATLAS-3200 Application                              | 32  |

|-----------|-----------------------------------------------------------|-----|

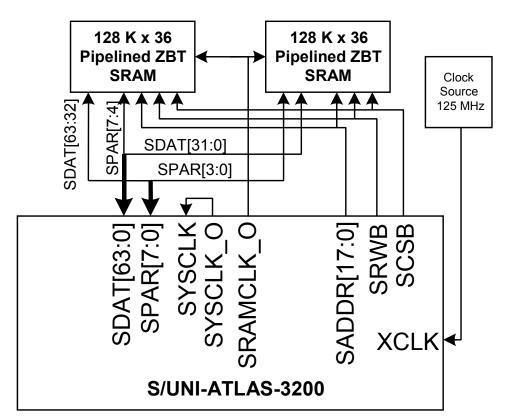

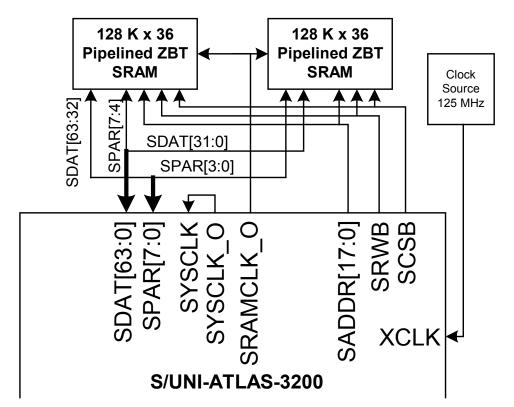

| Figure 2  | Interface between S/UNI-ATLAS-3200 and External RAM       | 33  |

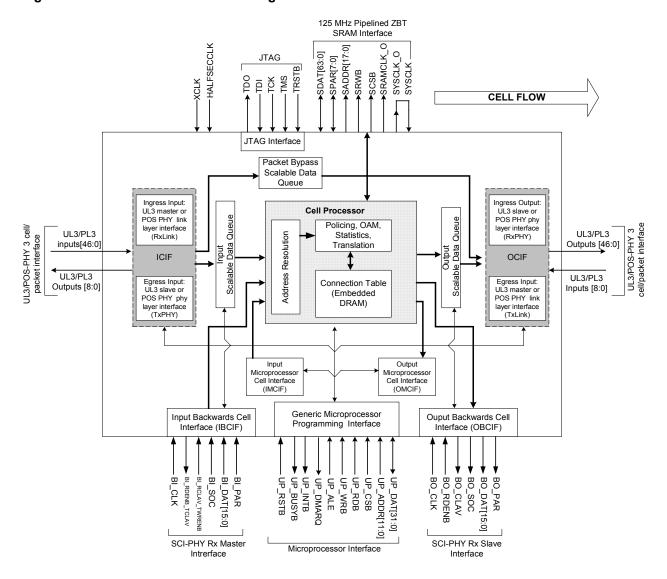

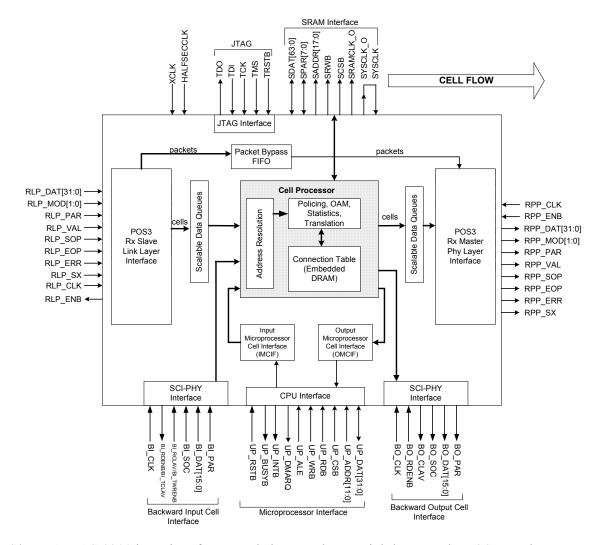

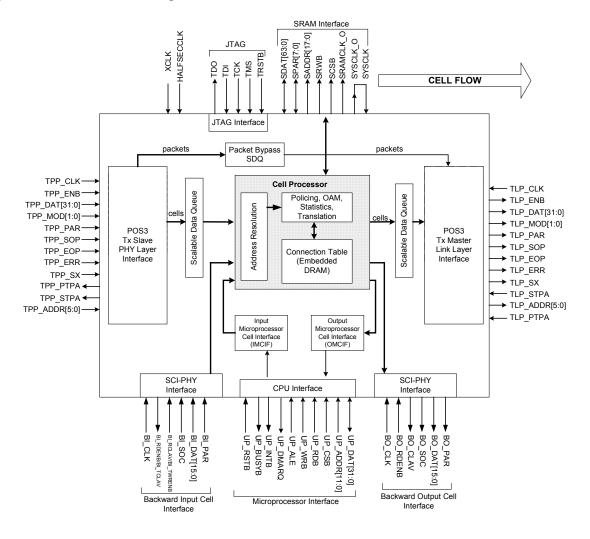

| Figure 3  | S/UNI-ATLAS-3200 Block Diagram                            | 34  |

| Figure 4  | Pin Diagram                                               | 38  |

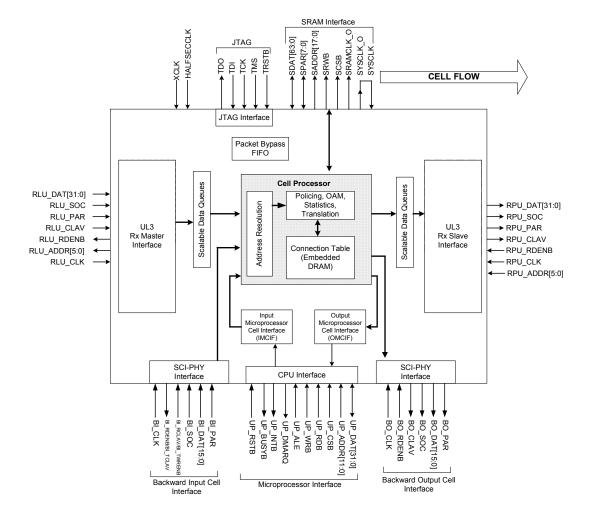

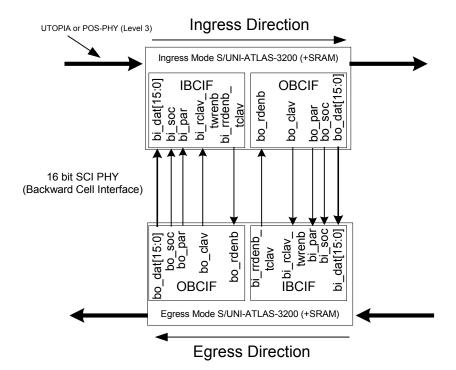

| Figure 5  | UTOPIA Level 3 Ingress Interface                          | 64  |

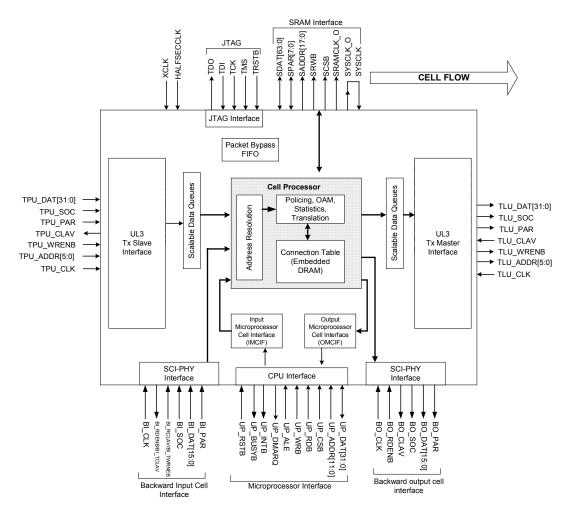

| Figure 6  | UTOPIA Level 3 Egress Interface                           | 65  |

| Figure 7  | POS-PHY Level 3 Ingress Interface                         | 67  |

| Figure 8  | POS-PHY Level 3 Egress Interface                          | 68  |

| Figure 9  | ATM Cell Format                                           | 73  |

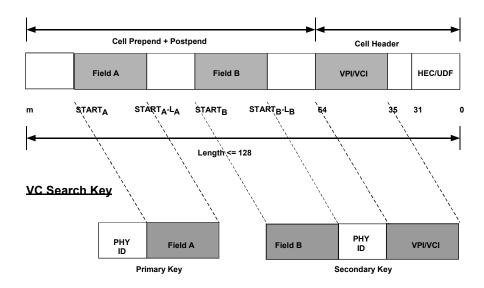

| Figure 10 | VC Search Key Extraction                                  | 74  |

| Figure 11 | Parameters of the Primary and Secondary Keys              | 75  |

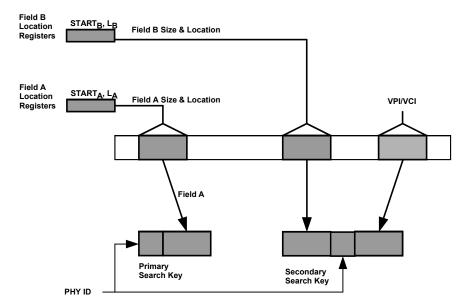

| Figure 12 | VC Search Key Construction                                | 76  |

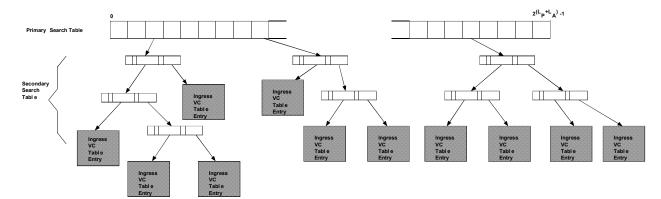

| Figure 13 | Construction of Primary and Secondary Keys                | 78  |

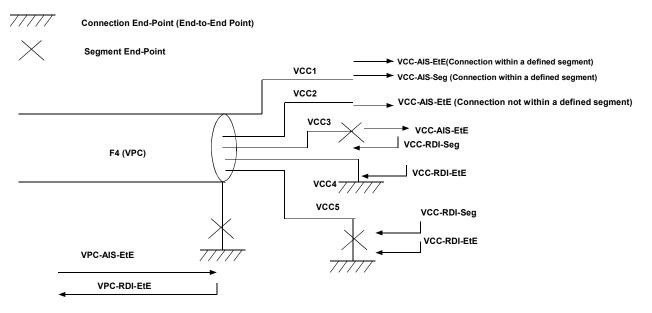

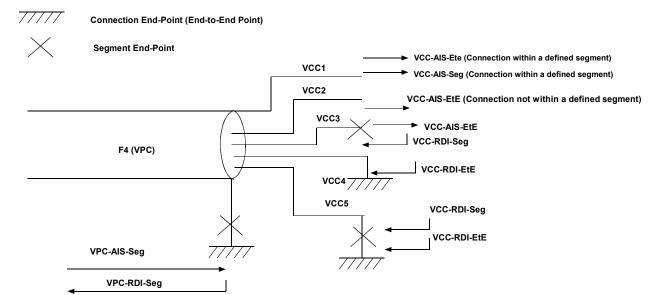

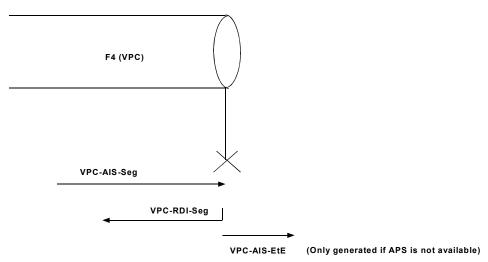

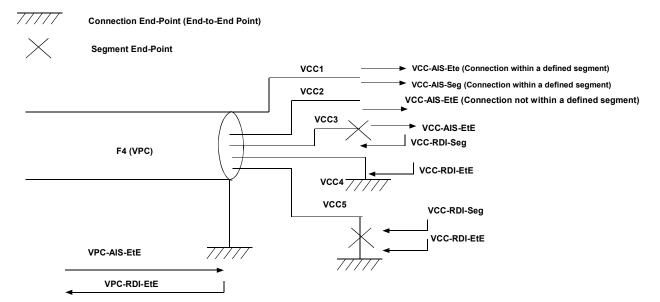

| Figure 14 | F4 to F5 OAM Flows                                        | 109 |

| Figure 15 | Termination of F4 Segment and End-to-End-Point Connection | 109 |

| Figure 16 | Termination of F4 Segment and End-to-End Point Connection | 111 |

| Figure 17 | Termination of F4 Segment End-Point Connection            | 112 |

| Figure 18 | Termination of F4 End-to-End Point Connection             | 113 |

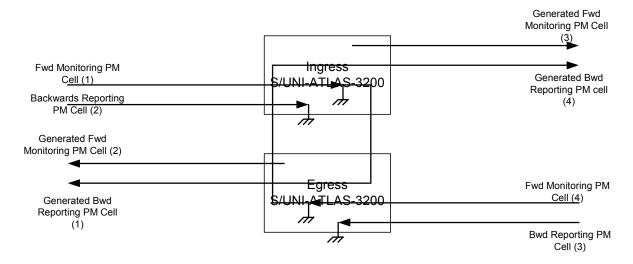

| Figure 19 | PM Flows                                                  | 119 |

| Figure 20 | Connection of S/UNI-ATLAS-3200 BCIFs                      | 135 |

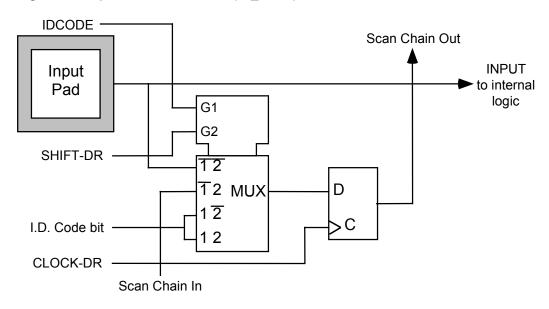

| Figure 21 | Input Observation Cell (IN_CELL)                          | 388 |

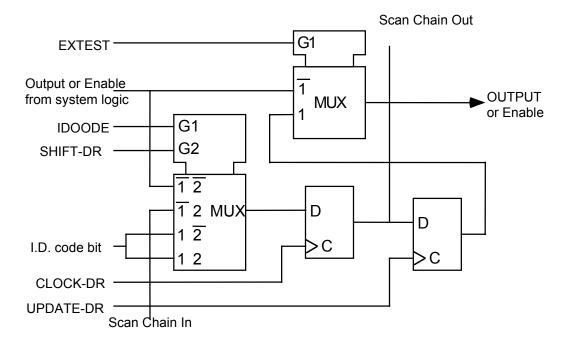

| Figure 22 | Output Cell (OUT_CELL)                                    | 388 |

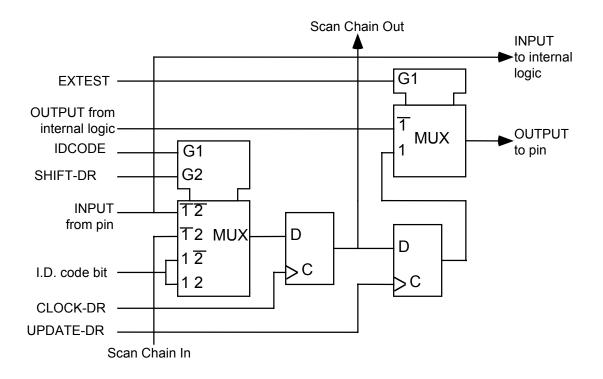

| Figure 23 | Bidirectional Cell (IO_CELL)                              | 389 |

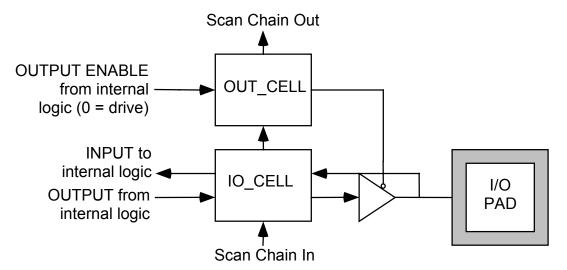

| Figure 24 | Layout of Output Enable and Bidirectional Cells           | 389 |

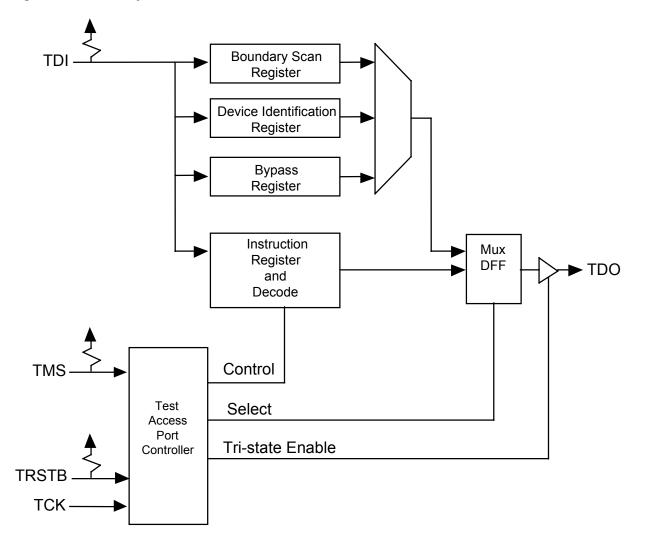

| Figure 25 | Boundary Scan Architecture                                | 393 |

| Figure 26 | TAP Controller Finite State Machine                       | 394 |

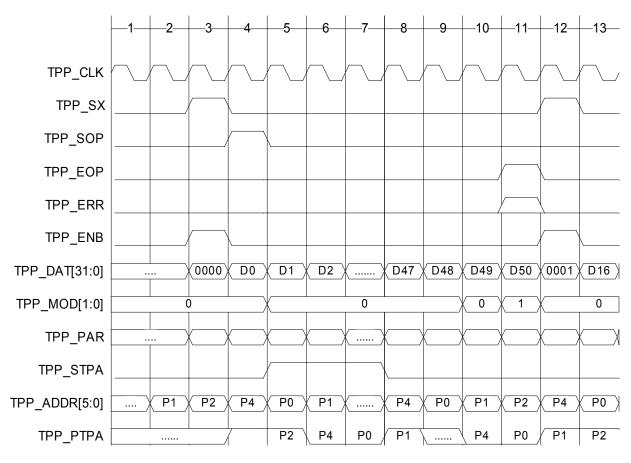

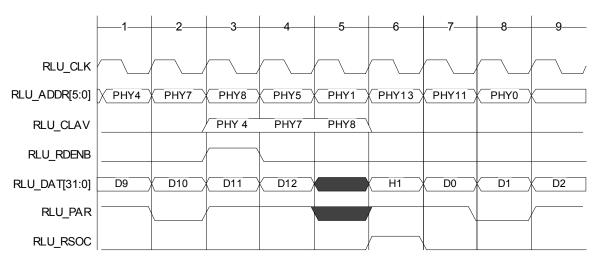

| Figure 27 | POS-PHY Level 3 Ingress Logical Timing                    | 398 |

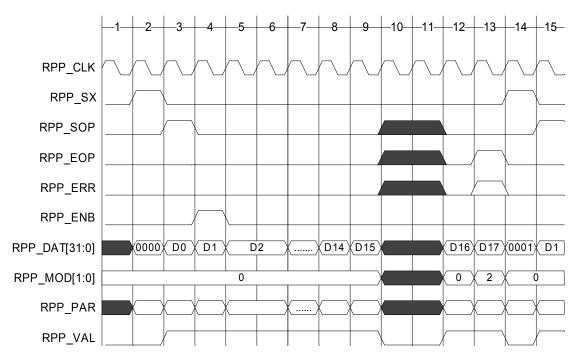

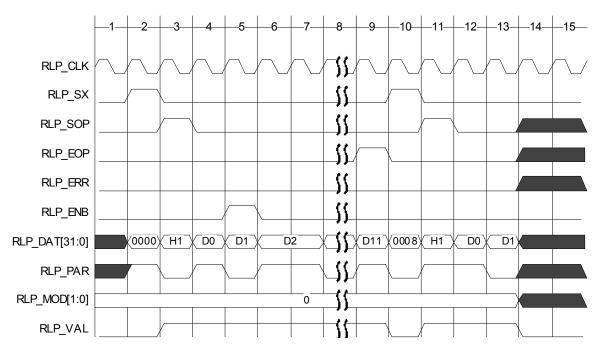

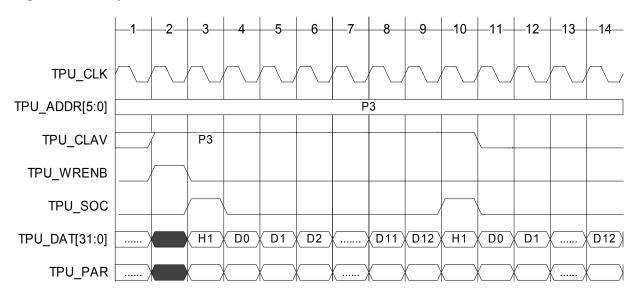

| Figure 28 | RxLink POS-PHY Packet Transfer                            | 399 |

| Figure 29 | RxLink back to back POS-PHY Packet Transfer               | 400 |

| Figure 30 | RxLink POS-PHY ATM Cell Transfer                          | 401 |

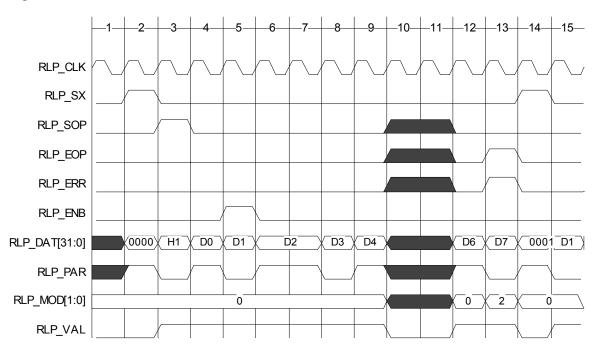

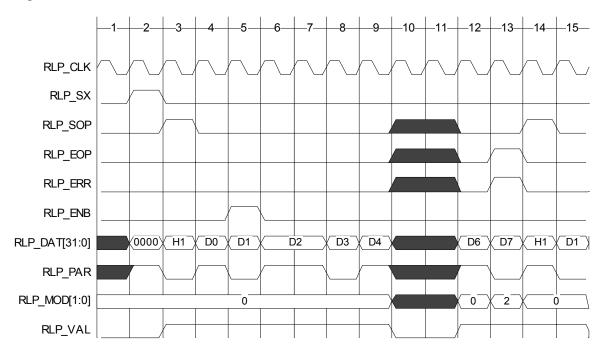

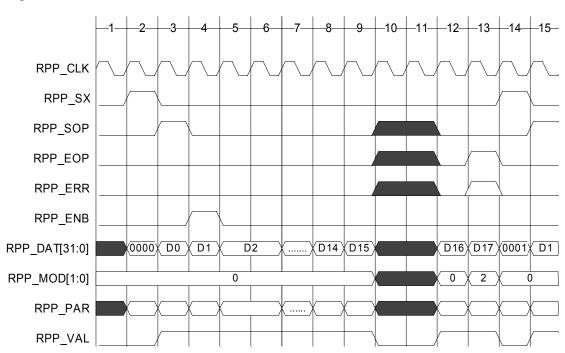

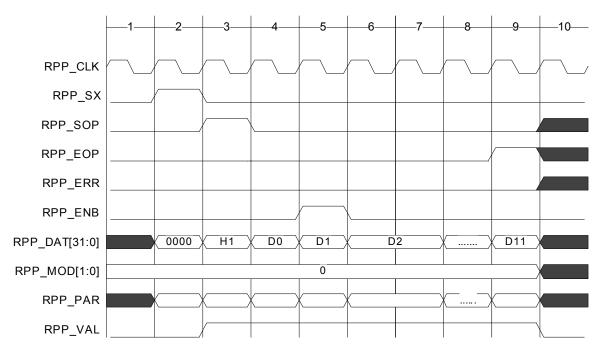

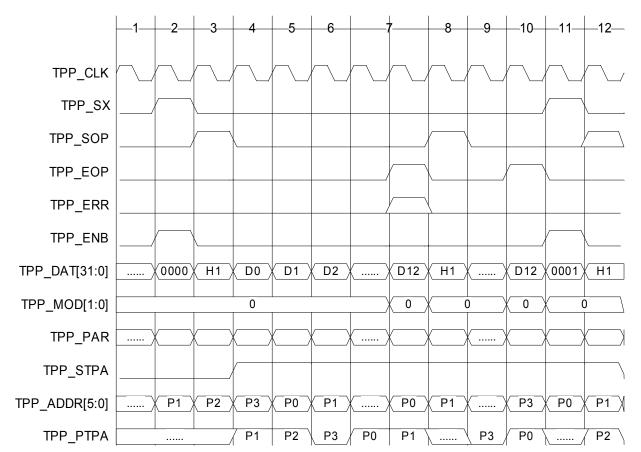

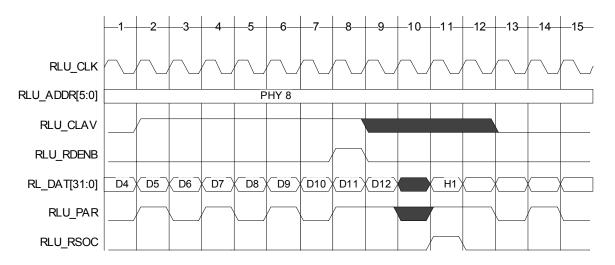

| Figure 31 | RxPHY POS-PHY Packet Transfer                             | 402 |

| Figure 32 | RxPhy POS-PHY ATM Cell Transfer                           | 403 |

| Figure 33 | POS-PHY Level 3 Egress Logical Timing                     | 404 |

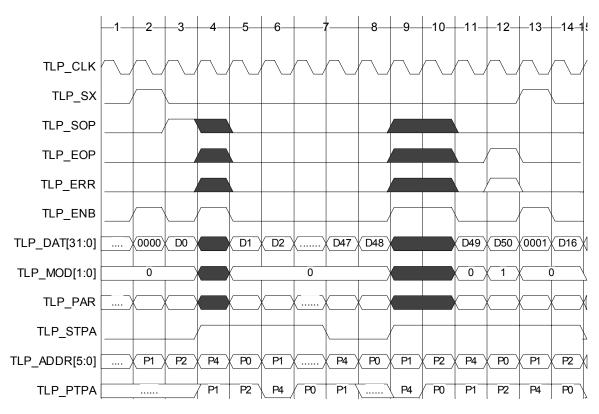

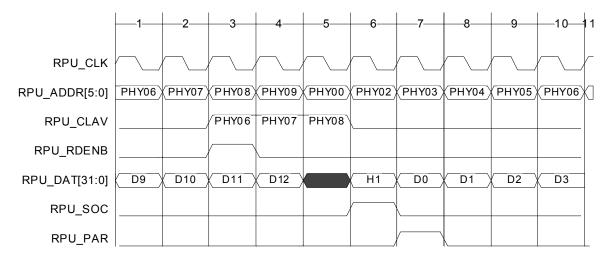

| Figure 34 | TXPhy POS-PHY Packet Transfer                       | 405 |

|-----------|-----------------------------------------------------|-----|

| Figure 35 | Transmit POS-PHY ATM Cell Transfer                  | 406 |

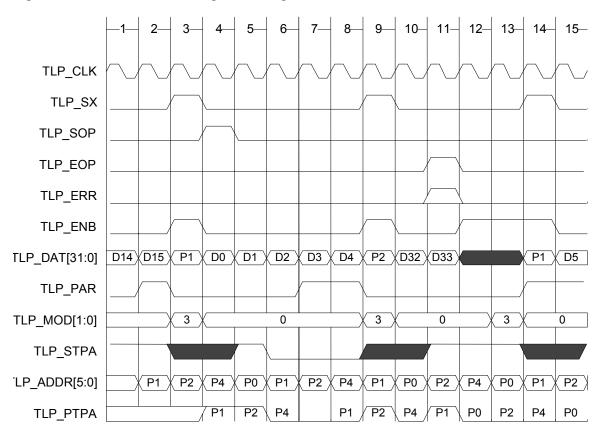

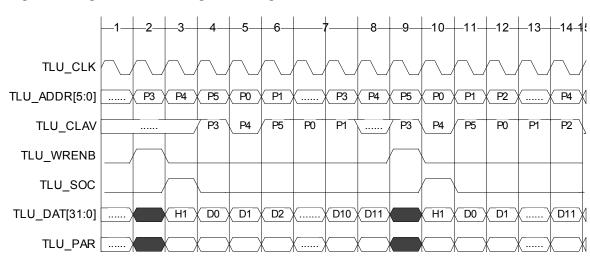

| Figure 36 | TxLink POS-PHY Logical Timing                       | 407 |

| Figure 37 | TxLink POS-PHY ATM Cell Transfer Timing             | 408 |

| Figure 38 | Ingress UTOPIA Logical Timing                       | 409 |

| Figure 39 | RxLink UTOPIA Cell Transfer                         | 410 |

| Figure 40 | RxLink Back-to-Back UTOPIA Cell Transfers           | 410 |

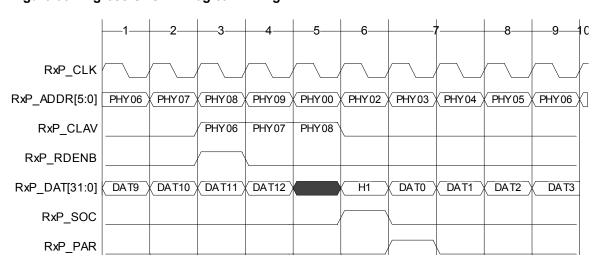

| Figure 41 | RxPhy UTOPIA Cell Transfer                          | 411 |

| Figure 42 | Egress UTOPIA Logical Timing                        | 412 |

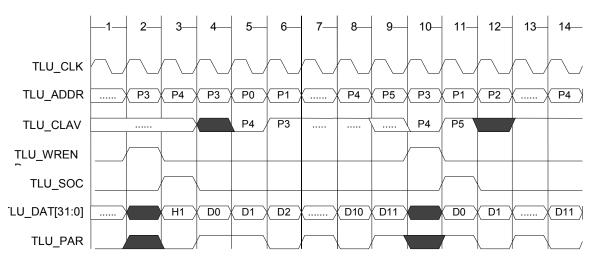

| Figure 43 | TxPhy UTOPIA Cell Transfer                          | 413 |

| Figure 44 | TxLink UTOPIA Transfer                              | 414 |

| Figure 45 | TxLink Back-to-Back UTOPIA Transfer                 | 414 |

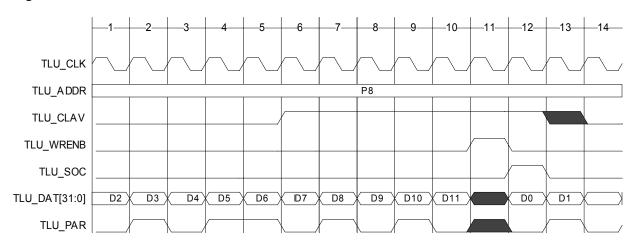

| Figure 46 | Interface between S/UNI-ATLAS-3200 and External RAM | 416 |

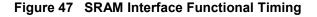

| Figure 47 | SRAM Interface Functional Timing                    | 416 |

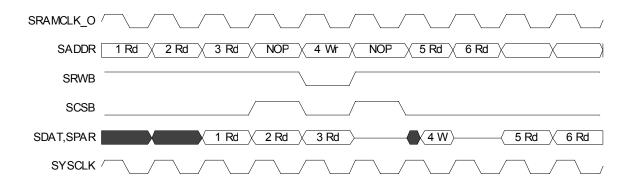

| Figure 48 | Normal BCIF Functional Timing                       | 417 |

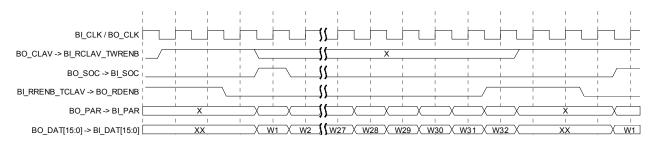

| Figure 49 | IBCIF as Tx Slave Functional Timing                 | 417 |

| Figure 50 | RSTB AC Timing                                      | 421 |

| Figure 51 | Half-Second Clock AC Timing                         | 421 |

| Figure 52 | Microprocessor Interface Read Access AC Timing      | 422 |

| Figure 53 | Microprocessor Interface Write AC Timing            | 424 |

| Figure 54 | UTOPIA Level 3 / POS-PHY Level 3 AC Timing          | 425 |

| Figure 55 | BCIF Interface AC Timing                            | 425 |

| Figure 56 | SRAM Interface AC Timing                            | 426 |

| Figure 57 | JTAG Port Interface AC Timing                       | 428 |

| Figure 58 | 768 Tape Ball Grid Array (TBGA)                     | 430 |

# **List of Tables**

| Table 1  | Signal Ball Assignment (Alphabetical)                       | 40  |

|----------|-------------------------------------------------------------|-----|

| Table 2  | Power/Ground Ball Assignment (Alphabetical)                 | 41  |

| Table 3  | Polling and Servicing Calendar Example                      | 69  |

| Table 4  | PHY Mapping                                                 | 71  |

| Table 5  | Search Table                                                | 77  |

| Table 6  | Secondary Search Table Fields                               | 78  |

| Table 7  | VC Linkage Table                                            | 79  |

| Table 8  | VC Record Table                                             | 80  |

| Table 9  | VC Table Fields used in Cell Processing                     | 81  |

| Table 10 | Status VC Table Field                                       | 81  |

| Table 11 | Configuration VC Table Field                                | 82  |

| Table 12 | Internal Status VC Table Field                              | 84  |

| Table 13 | OAM Configuration VC Table Field                            | 86  |

| Table 14 | VC Table Miscellaneous Fields                               | 88  |

| Table 15 | VC Table Fields For Header Translation                      | 90  |

| Table 16 | VC Table Policing Fields                                    | 91  |

| Table 17 | Policing Configuration VC Table Field                       | 92  |

| Table 18 | Policing Actions                                            | 96  |

| Table 19 | Actions on Policing with COCUP=0                            | 96  |

| Table 20 | Actions on Policing with COCUP=1                            | 97  |

| Table 21 | Non-Compliant Cell Count Configurations                     | 97  |

| Table 22 | Actions with per-PHY Policing                               | 98  |

| Table 23 | Internal Per-PHY Policing RAM                               | 99  |

| Table 24 | Per-PHY Policing Actions                                    | 99  |

| Table 25 | Per-PHY Policing Non-Compliant Count Options                | 100 |

| Table 26 | Per-PHY/Per-VC Non-Compliant Cell Counting PHYVCCount=0     | 100 |

| Table 27 | Per-PHY and per-VC Non-Compliant Cell Counting PHYVCCount=1 | 101 |

| Table 28 | F4 to F5 Fault Management Processing                        | 114 |

| Table 29 | Linkage Table Fields Used in PM                             | 118 |

| Table 30 | PM Activation Fields                                        | 118 |

| Table 31 | Performance Management Record Table                         | 121 |

| Table 32 | PM Table Configuration Field                                | 122 |

| Table 33 | QOS Parameters for Performance Management                   | 124 |

| Table 34 | Change of State FIFO                                 | 129 |

|----------|------------------------------------------------------|-----|

| Table 35 | Count Rollover FIFO Format For Per-VC Count Entries  | 131 |

| Table 36 | Count Rollover FIFO Format For Per-PHY Count Entries | 131 |

| Table 37 | Count Rollover FIFO Format For PM Entries            | 132 |

| Table 38 | Backwards Cell Interface Cell Format                 | 136 |

| Table 39 | BCIF Cell Information Field                          | 137 |

| Table 40 | Microprocessor Cell Information Field                | 141 |

| Table 41 | Suggested FIFO Size Encoding                         | 329 |

| Table 42 | Suggested FIFO Size Encoding                         | 360 |

| Table 43 | Suggested FIFO Size Encoding                         | 371 |

| Table 44 | Test Mode Register Memory Map                        | 376 |

| Table 45 | Test Mode 0 Read Map                                 | 378 |

| Table 46 | Test Mode 0 Write Map                                | 379 |

| Table 47 | Instruction Register                                 | 380 |

| Table 48 | Identification Register                              | 380 |

| Table 49 | Boundary Scan Register                               | 380 |

| Table 50 | Suggested FIFO Size Encoding                         | 390 |

| Table 51 | SDQ-ATLAS Configuration Example                      | 391 |

| Table 52 | Absolute Maximum Ratings                             | 418 |

| Table 53 | DC Characteristics                                   | 419 |

| Table 54 | RTSB AC Timing                                       | 421 |

| Table 55 | Half-Second Clock AC Timing                          | 421 |

| Table 56 | Microprocessor Interface Read Access AC Timing       | 421 |

| Table 57 | Microprocessor Interface Write Access AC Timing      | 423 |

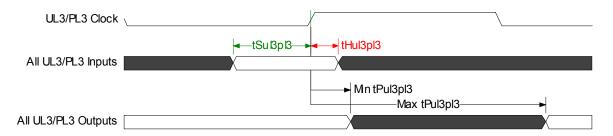

| Table 58 | UTOPIA Level 3 / POS-PHY Level 3 AC Timing           | 424 |

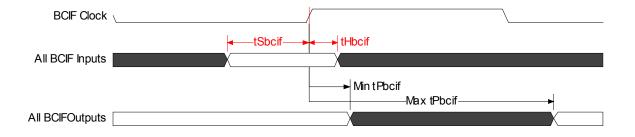

| Table 59 | BCIF Interface AC Timing                             | 425 |

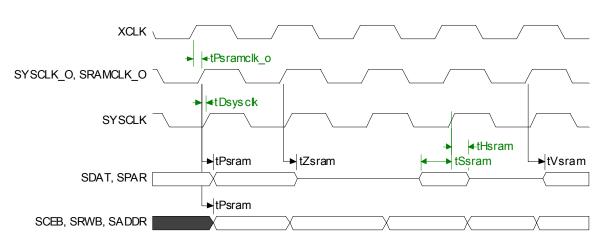

| Table 60 | SRAM Interface AC Timing                             | 426 |

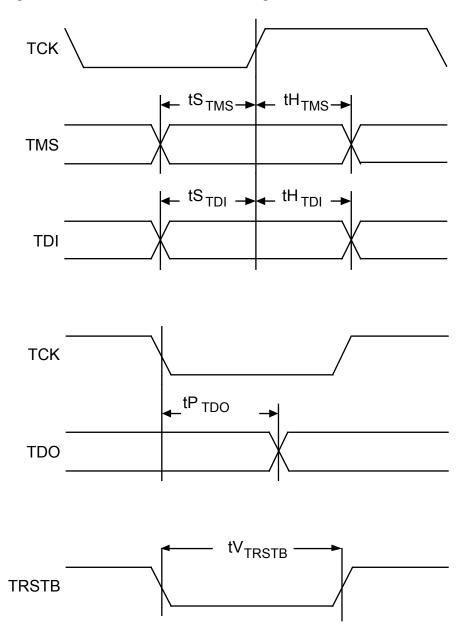

| Table 61 | JTAG Port Interface Timing                           | 426 |

| Table 62 | Ordering Information                                 | 429 |

# 1 Definitions

This table defines the acronyms used in this data sheet.

| Acronym | Definition                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AIS     | Alarm Indication Signal. AlS cells are OAM Fault Management cells whose Function Type fields identify them as AIS cells as per ITU-T I.610. They are sent once per second by an ATM Network Element which has detected certain error conditions, such as a loss of continuity. AIS alarm refers to the detection that the S/UNI-ATLAS-3200 is receiving AIS cells on a particular VC.                                    |

| ВТ      | <b>Burst Tolerance.</b> The burst tolerance is a policing parameter that indicates the maximum length of a burst (at the peak allowable cell rate) that is permitted before the Sustained Cell Rate test will be violated.                                                                                                                                                                                               |

| Bwd PM  | <b>Backwards Performance Management Cell.</b> These PM OAM cells are sent by a PM session on reception of a Fwd PM cell, and carry data about the cell flow as observed by both the start and end point of the PM flow.                                                                                                                                                                                                  |

| Bwd LB  | Backwards, or Returned Loopback Cell. An OAM Loopback cell whose Loopback Indication bit is zero, indicating it has already been looped back.                                                                                                                                                                                                                                                                            |

| CBR     | <b>Constant Bit Rate.</b> CBR service is one of the standard traffic contracts, in which a constant, unchanging amount of bandwidth is guaranteed to the user, with time-of-delivery guarantees. Voice traffic is a classic use of CBR service                                                                                                                                                                           |

| CDV     | <b>Cell Delay Variation.</b> The CDV Tolerance is one of the parameters that determines the policing parameters, particularly the Limit parameter of the Peak Cell Rate test.                                                                                                                                                                                                                                            |

| CLP     | <b>Cell Loss Priority.</b> This is a field in the header of an OAM cell. High-priority cells are those with CLP = 0, and are sometimes referred to as CLP0 cells. Low priority blocks are sometimes referred to as CLP1 cells, and the aggregate flow is referred to as CLP0+1.                                                                                                                                          |

| CC      | Continuity Check. CC cells are OAM Fault Management cells whose Function Type fields identfy them as CC cells as per ITU-T I.610. They are sent once per second by a flow start point in the absence of user traffic, to indicate that the connection remains active. CC alarm refers to the detection that a VC on the S/UNI-ATLAS-3200 has received neither user cells nor CC cells for a nominal period of 3 seconds. |

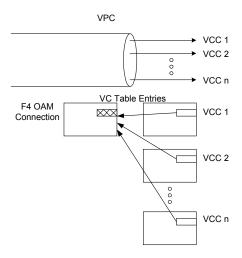

| F4      | The F4 OAM Layer is the OAM Layer associated with the Virtual Path. In S/UNI-ATLAS-3200, a VC may be part of an F4 flow or an F5 flow. In the case of an F4 flow being sourced or terminated, a number of VCs which form part of F5 flows may have an associated F4 OAM VC, which performs the OAM for the F4 flow. This F4 OAM VC is specified by the VPC Pointer in the Linkage Table.                                 |

| F5      | The F5 OAM Layer is the OAM Layer associated with the Virtual Channel.                                                                                                                                                                                                                                                                                                                                                   |

| FM      | <b>Fault Management.</b> Fault Management OAM cells include AIS cells, RDI cells, CC cells, and LB cells.                                                                                                                                                                                                                                                                                                                |

| Fwd LB  | A Forward, or Parent, Loopback cell. An OAM Loopback cell whose Loopback Indication bit is 1, indicating it has not yet been looped back.                                                                                                                                                                                                                                                                                |

| Fwd PM  | Forward Performance Management cell. These PM OAM cells are sent by a PM session at an OAM start point every N cells, where N is a programmable number ranging from 128 to 32K. They contain information about the cell flow on a VC as seen by the transmitting point.                                                                                                                                                  |